打开文本图片集

摘要:锁相环频率综合器关键技术作为电路设计的理论技术,发挥着重要的作用。本文主要针对锁相环频率综合器工作原理和系统结构进行分析,着重介绍了其中几种关键性的技术,内容如下。

关键词:锁相环频率综合器;关键技术;研究

1锁相环频率综合器的基本结构

锁相环是一种控制系统,该控制系统属于相位负反馈控制系统。在此种控制系统的作用下,相位输出信号和压控振荡器的频率可保持一定联系。并能对输入信号中的噪声和压控振荡器中的相位噪声进行抑制。其中模拟锁相环和数字锁相环是锁相环的两种常见形式。其中锁定状态下跟踪过程和失所后锁定进入的捕捉过程是锁相环两种主要的工作形式。处于锁定状态下的输入信号和压控振荡器之间的相位差是比较小的,因此此种情况可采取线性系统对跟踪过程进行处理。处于捕捉状态下的输入信号和压控振荡器之间的相位差是比较大的。在相位差变化幅度较大的情况下,会超出锁相环各部件工作范围。该过程属于非线性的,因此在分析方法的选择上需要选取非线性系统分析方法。其中压控振荡器、鉴频鉴相器、分频器、环路滤波器以及晶体振荡器是基于锁相环频率综合器的基本结构[1]。

2锁相环频率综合器的基本原理

分析锁相环频率综合器的基本原理需要从晶体振荡器、鉴频鉴相器、环路滤波器以及压控振荡器上分析。其中频率稳定度较高、相位噪声较低的为晶体振荡器,晶体振荡器是数字电路和射频电路的重要组成部件。在石英晶体振荡器基础上,若采用33MHZ的石英晶体振荡器可以起到增大相位噪声功能和降低功耗的作用。此外,锁相环频率综合器中另一项重要的组成部分为鉴频鉴相器。鉴频鉴相器的主要作用是将晶体振荡器的输出参考频率、分频器输出频率和相位进行比较,在此基础上出现两种信号的电压误差信号。若锁相环处于工作状态,晶体振荡器的输出参考频率和分频器输出频率相比相差较大时,环路滤波器和鉴频鉴相器会同时工作,将压控振荡器的控制电压改变,此时晶体振荡器的输出参考频率和分频器输出频率会非常接近。比较鉴频鉴相器两个信号的条件为晶体振荡器的输出参考频率和分频器输出频率接近程度较大。对环路中低频噪声起到滤除作用的为环路滤波器。环路滤波器除了以上作用外,还可以将加载压控振荡器上的噪声电压减小,并将锁相环频率综合器的动态特性建立起来。其中极点个数决定环路滤波器的阶数。压控振荡器在零频率上会引入一个极点,因此环路滤波器阶数要比整个锁相环频率综合器阶数少一个。针对此种情况,在实际设计中国会将零点引入,这样可以保障整体环路中相位裕量足够。锁相环频率综合器中的核心版块为压控振荡器,其中输出频率大小可以采用输入电压函数来表示。如fout=f0+KvcoVctrl,中心频率表示为f0,压控振荡器增益表示为Kvco,输入电压表示为Vctrl,振荡器输出频率为fout。将高频输出信号在一定分频系数下进行分频是分频器的主要作用。分频器是压控振荡器完整负反馈环路的重要组成元件。在实际工作中利用分频器可以反复切换各个信号,对不同输出频率进行调节[2]。

3锁相环频率综合器的噪声分析

电力电路中的噪声均可以将其看成目的信号之外,所有信号的总称。锁相环频率综合器中的噪声可以是任何不希望的电流、电压波动所产生的声音。电子元件、系统和网络中都存在不同程度的噪声。噪声的存在对信号质量会产生影响。并对电子系统的测量、计算精度产生影响。此外也会影响电力方法处理信号的大小。其中电路噪声有不同的分类,如闪烁噪声、热噪声以及散弹噪声等。不同类型的噪声产生原因和传播方式不一,因此采取的减弱和消除方法也是不一樣的。锁相环受噪声的干扰会影响其正常工作。其中环路器本身产生的噪声。伴随信号进入环路器中的噪声以及压控振荡器控制端感应寄生到的噪声是噪声产生的主要来源。环路正常工作状态会受到噪声的影响,因此需要加强环路性能受噪声影响的分析,以便可以找到减弱噪声的方法[3]。

3.1鉴频鉴相器的噪声分析

锁相环频率综合器中作为关键电路模块之一的就是鉴频鉴相器。其中较强的非线性是鉴频鉴相器具有的特征之一。基波分量、二次谐波以及高次谐波分量是输入到这个电路所有信号在输出时包含的内容。分析鉴频鉴相器相位噪声,主要来源于以下几方面。一方面的噪声是鉴频鉴相器自身引入产生,另一方面的是鉴频鉴相器输入外加噪声产生的。其中如何减小鉴频鉴相器噪声对锁相环的影响,可以采取以下方式,方案一:将鉴频鉴相器的鉴相灵敏度增大,并将压控振荡器的压控灵敏度也减小。此种情况下可以将边带抑制能力提升。方案二:将鉴频鉴相器的频率提高,将鉴频鉴相器输入信号的幅值减小。以上两种方案均可以将鉴频鉴相器噪声对锁相环的影响作用减小[4]。

3.2压控振荡器的噪声分析

锁相环中作为核心的线路为压控振荡器,其中压控振荡器噪声性能直接影响锁相环的噪声性能。对压控振荡器进行研究时需要将以下因素考虑进去。一种是控制信号的噪声因素,另一种是压控振荡器本身的噪声。压控振荡器针对锁相环来说,高通滤波器特性是压控振荡器噪声特有的性能。之所以这样说是因为将低通作用加入到环路中,压控振荡器的噪声可以削弱。如何减少压控振荡器的噪声,将噪声对锁相环的影响削弱,可以采取以下方案。方案一:将压控振荡器自身存在的噪声减小,之后在将环路中的输入参考信号的噪声减小,最后环路带宽内尽可能满足Hc(jwm)≈1,此时压控振荡器的噪声会显著减小。方案二:环路带宽在选择时,优先选择可以对压控振荡器噪声进行控制的环路带宽,该形式的噪声减小方法也可以发挥对抑制压控振荡器控制端干扰的作用[5]。

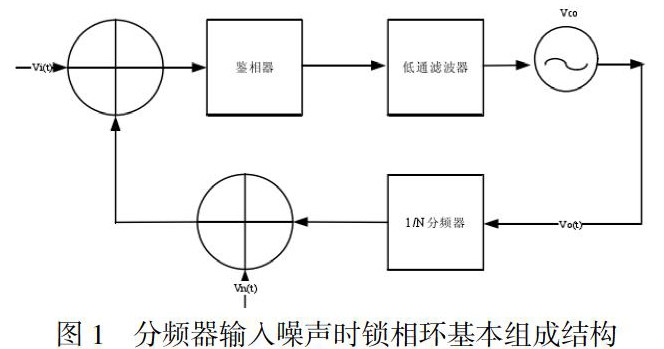

3.3分频器的噪声分析

下图是分频器输入噪声时锁相环基本组成结构,根据下图可知此时相位噪声谱密度函数为SØ0=(Wm)=N2[SØi(Wm)-SØN(Wm)]/Hc(jWm)/2,且锁相环中引入分频系数N分频器时,可以将倍频器看成压控振荡器。尤其是在低频率偏离的情况下,此时Hc(jwm)≈1,SØN(Wm) 4结语 综上所述,以上是笔者针对基于锁相环频率综合器关键技术的相应分析,重点分析了锁相环频率综合器的工作原理和组成结构,以及探讨了其中关键性的技术,做各个模块的噪音性能进行了讨论,希望通过本文对锁相环频率综合器关键技术的研究有一定的帮助。 参考文献 [1]赵莉.基于锁相环的频率综合器关键技术研究[D].江苏:南京邮电大学,2013. [2]孙天慧.多模CMOS频率综合器关键模块设计及其整体优化[D].江苏:东南大学,2017. [3]白振强.小型化数字式频率合成器的设计与实现[D].四川:电子科技大学,2016. [4]付宇鹏.面向60GHz分数型锁相环应用的分数分频器的设计[D].江苏:东南大学,2016.